#### ATPESC 2021 August 8, 2021

# SW/HW Innovations in Emerging DL Training Systems

Urmish Thakker Principal Engineer

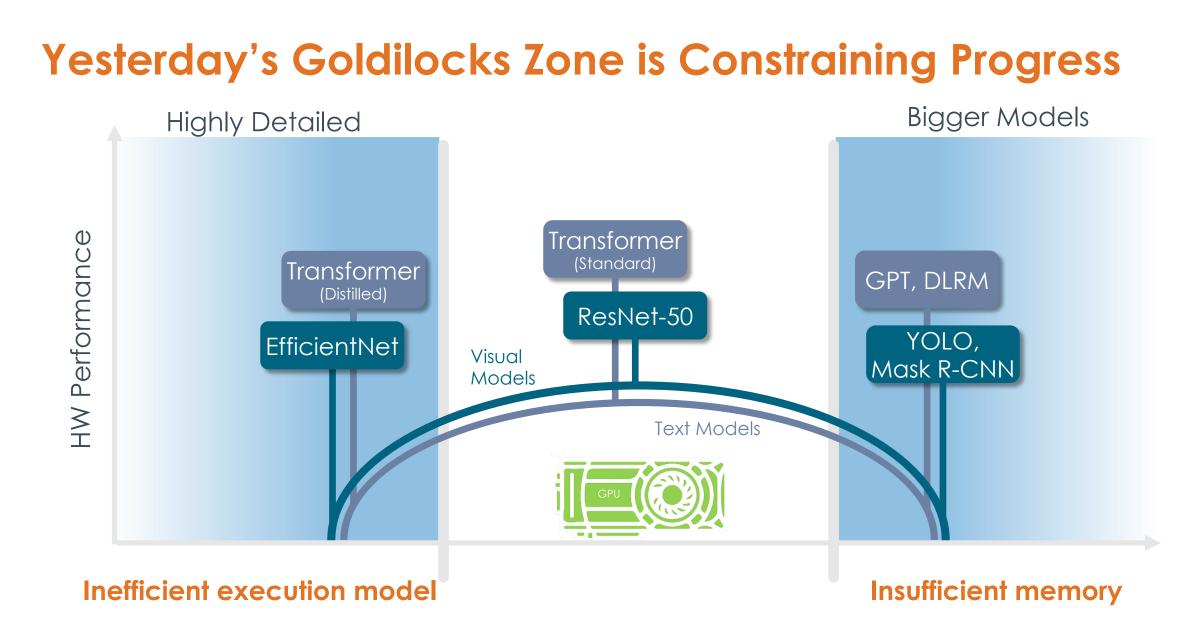

#### Goldilocks Zone

Too Hot

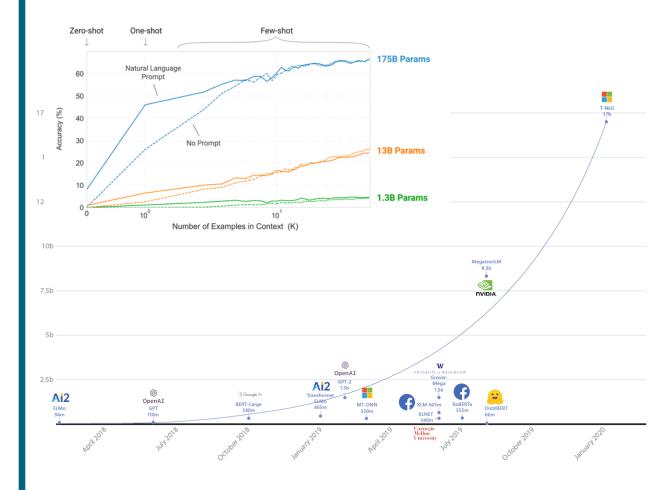

### **Trend of SOTA Models**

#### **TinyBERT: Distilling BERT for Natural Language Understanding**

Xiaoqi Jiao<sup>1\*†</sup> Yichun Yin<sup>2\*‡</sup> Lifeng Shang<sup>2‡</sup>, Xin Jiang<sup>2</sup> Xiao Chen<sup>2</sup>, Linlin Li<sup>3</sup>, Fang Wang<sup>1‡</sup> and Qun Liu<sup>2</sup> <sup>1</sup>Key Laboratory of Information Storage System, Huazhong University of Science and Technology, Wuhan National Laboratory for Optoelectronics <sup>2</sup>Huawei Noah's Ark Lab

{yin

{che} DistilBERT, a distilled version of BERT: smaller,

faster, cheaper and lighter

Victor SANH, Lysandre DEBUT, Julien CHAUMOND, Thomas WOLF Hugging Face {victor,lysandre,julien,thomas}@huggingface.co

#### Bigger Models

160

180

140

# **Our Mission**

Shaping the next-generation ML / DL computing system to accelerate the full model spectrum

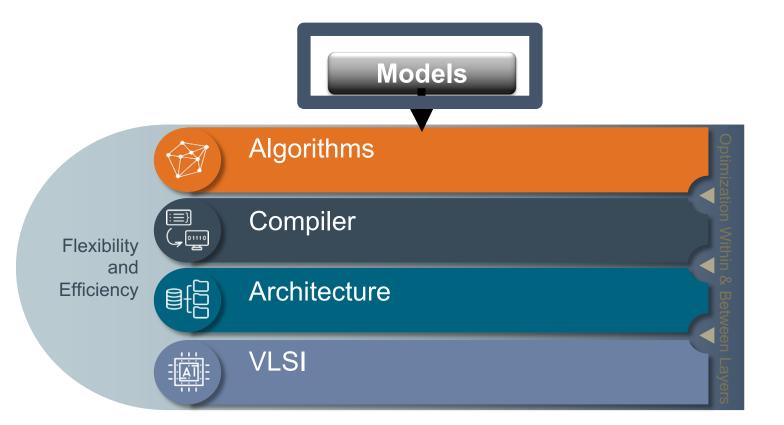

# How do we break out of the Godilocks Zone?

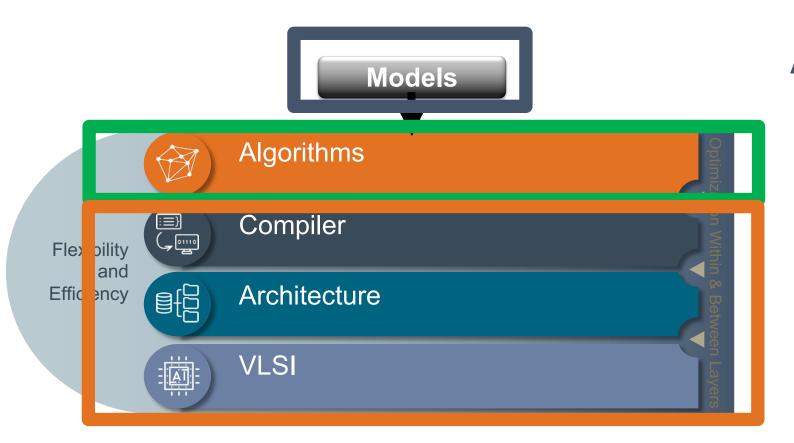

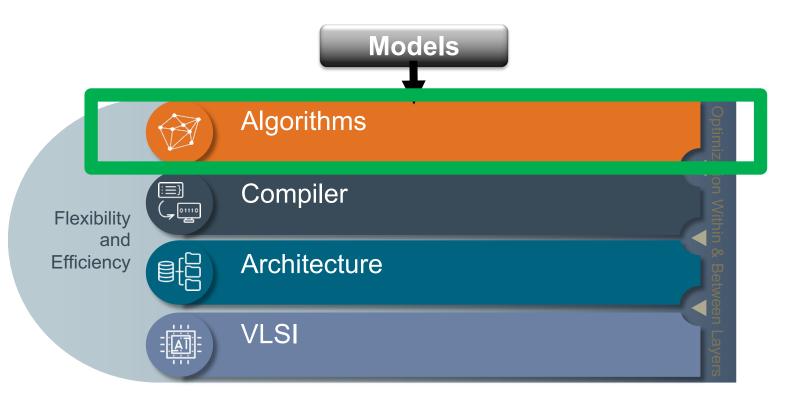

Fundamental advances required at all layers of the SW/HW stack.

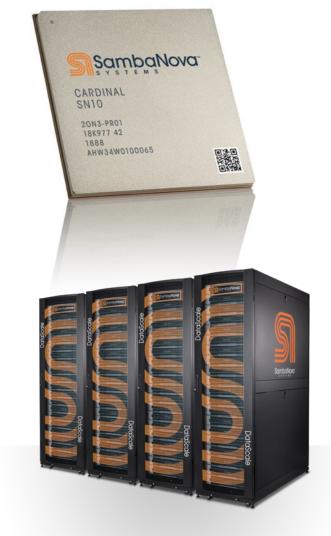

### The SambaNova Systems Advantage

#### **Application innovations**

#### High model accuracy

#### High compute efficiency

## Part 1.

# Enabling higher compute efficiency

©2021 SambaNova Systems

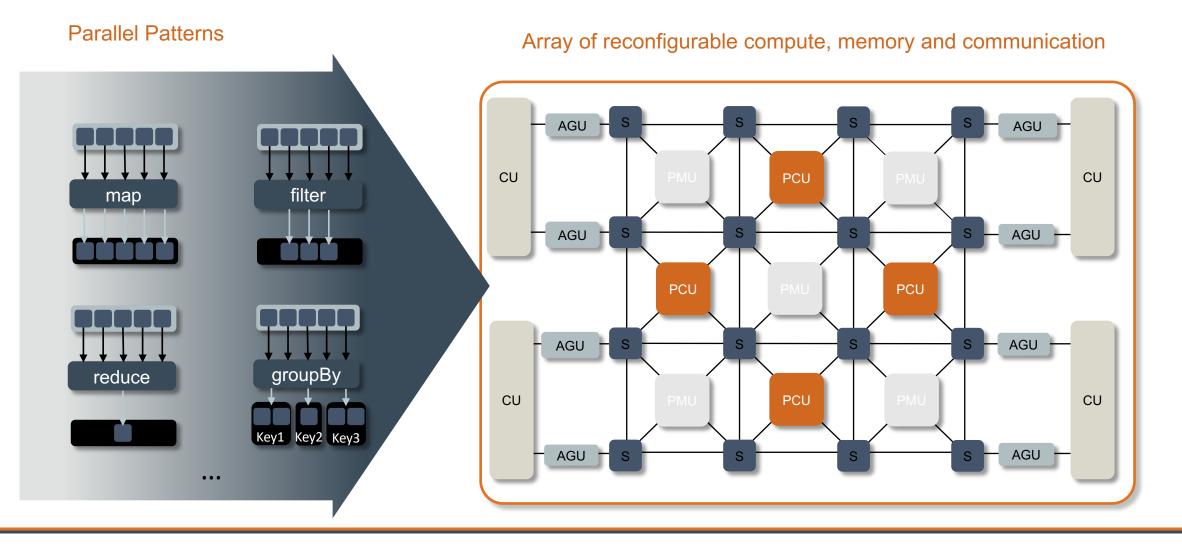

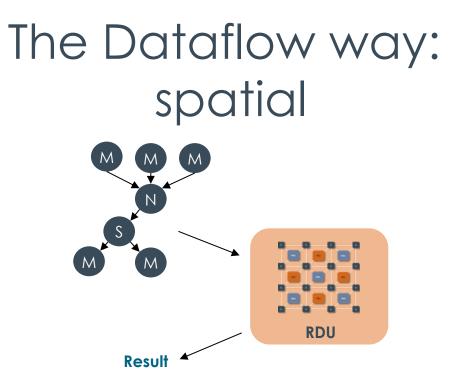

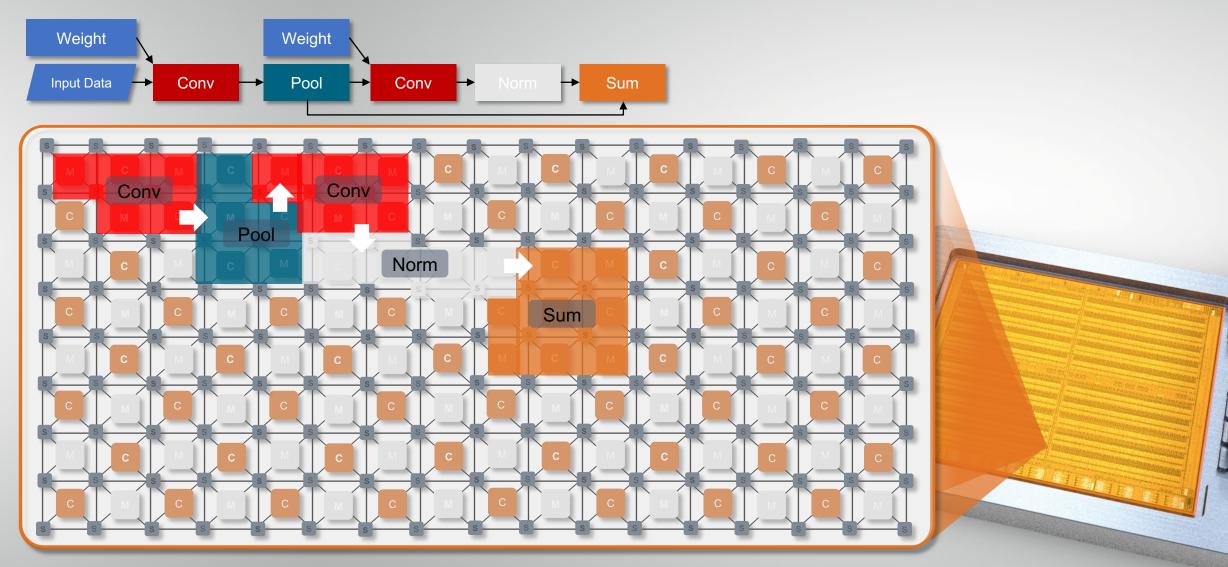

### Architecture: Reconfigurable Dataflow Unit (RDU)

Spatial Dataflow Within an RDU

#### The old way: kernel-by-kernel

# SambaFlow eliminates overhead and maximizes utilization

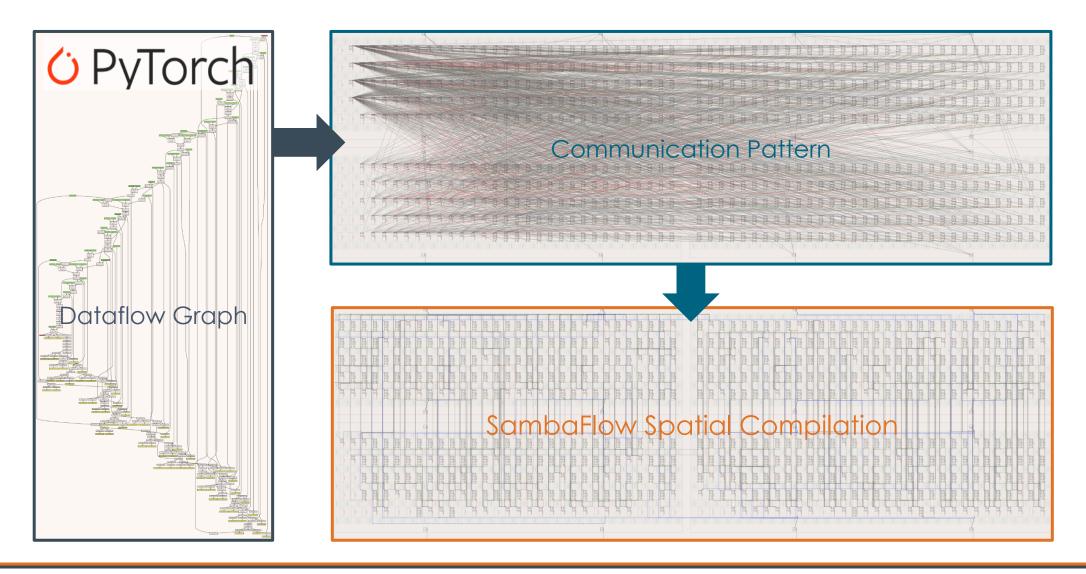

### Rapid Dataflow Compilation to RDU

©2021 SambaNova Systems

### SambaFlow Produces Highly Optimized Spatial Mappings

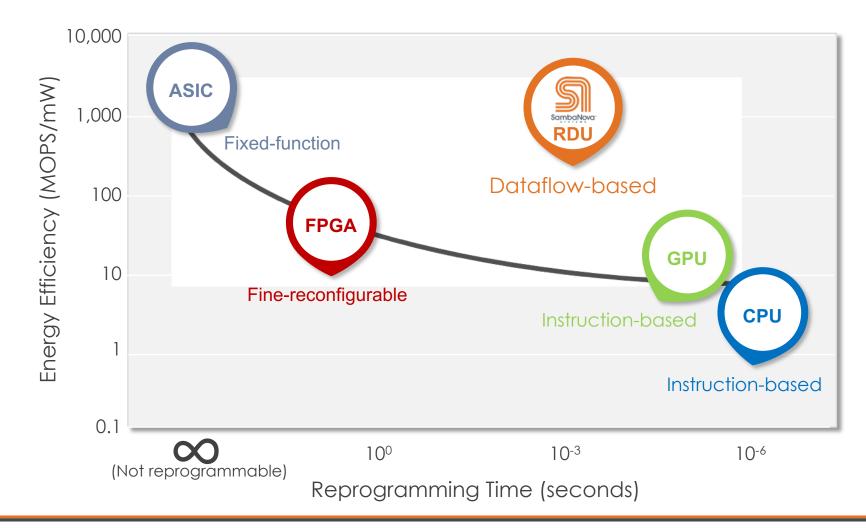

#### Uncompromised Programmability and Efficiency Breaking out of the programmability vs. efficiency tradeoff curve

### The SambaNova Systems Advantage

Achieve low time-to-accuracy

#### High model accuracy

# Part 2. High model accuracy:

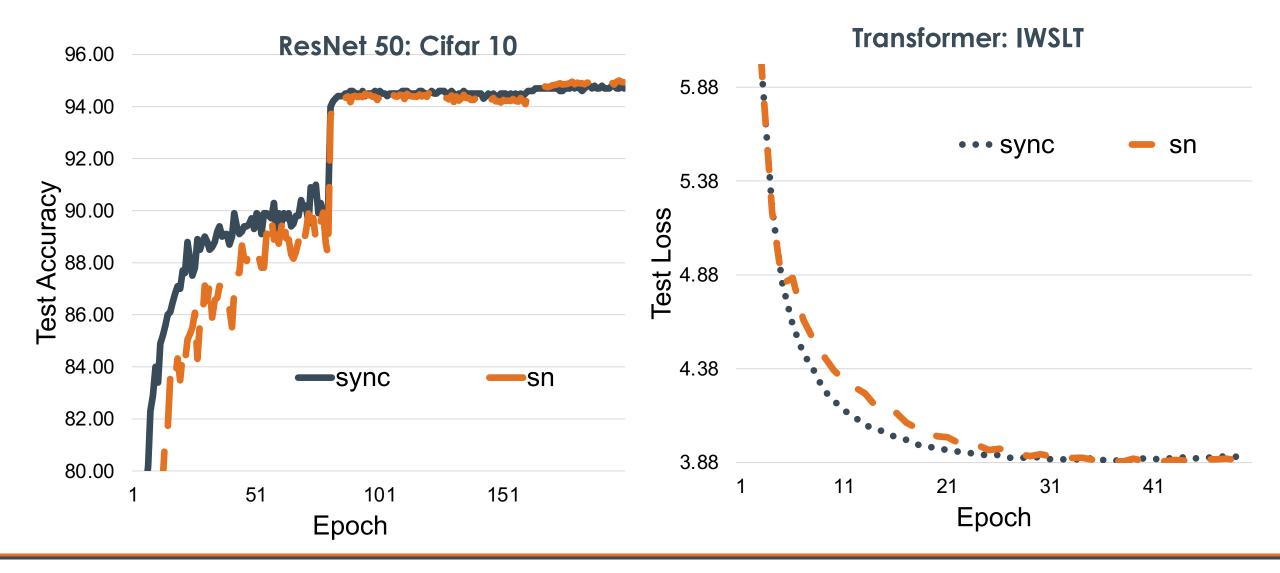

### + Pure 16-bit FPU training + Asynchronous pipeline parallelization

©2021 SambaNova Systems

### Low Precision (< 32-bit) Training

Binarized Neural Networks: Training Neural Networks with Weights and Activations Constrained to +1 or -1

Matthieu Courbariaux\*<sup>1</sup> Itay Hubara\*<sup>2</sup> Daniel Soudry<sup>3</sup> Ran El-Yaniv<sup>2</sup> Yoshua Bengio<sup>1,4</sup> <sup>1</sup>Université de Montréal <sup>2</sup>Technion - Israel Institute of Technology <sup>3</sup>Columbia University <sup>4</sup>CIFAR Senior Fellow \*Indicates equal contribution. Ordering determined by coin flip. MATTHIEU.COURBARIAUX @ GMAIL.COM ITAYHUBARA @ GMAIL.COM DANIEL.SOUDRY @ GMAIL.COM RANI@ CS.TECHNION.AC.IL YOSHUA.UMONTREAL @ GMAIL.COM

#### Recurrent Neural Networks With Limited Numerical Precision

Joachim Ott\*, Zhouhan Lin<sup>‡</sup>, Ying Zhang<sup>‡</sup>, Shih-Chii Liu\*, Yoshua Bengio<sup>‡†</sup> \*Institute of Neuroinformatics, University of Zurich and ETH Zurich ottj@ethz.ch, shih@ini.ethz.ch <sup>‡</sup>Département d'informatique et de recherche opérationnelle, Université de Montréal <sup>†</sup>CIFAR Senior Fellow {zhouhan.lin, ying.zhang}@umontreal.ca

Training Deep Neural Networks with 8-bit Floating Point Numbers

Naigang Wang, Jungwook Choi, Daniel Brand, Chia-Yu Chen and Kailash Gopalakrishnan IBM T. J. Watson Research Center Yorktown Heights, NY 10598, USA {nwang, choij, danbrand, cchen, kailash}@us.ibm.com

#### Higher system efficiency, minimal impact on acc. for specific models

### Efficiency of Low Precision Floating-point-units (16 vs. 32-bit)

#### 1.5X lower chip area

#### 3X higher energy efficiency

#### **1.5X** higher throughput

1. Horowitz. ISSCC 2014

2. Galal et. al. ISCA 2013

### Mixed Precision for Generic DL Training (16 + 32 bits FPU)

| NVIDIA / apex lines 52.5k                           |                                            | O PyTorch                                             |

|-----------------------------------------------------|--------------------------------------------|-------------------------------------------------------|

| A PyTorch Extension: Tools for easy mixed precision |                                            | Table of Contents                                     |

| 述 BSD-3-Clause License<br>☆ 4.7k stars 양 632 forks  | $\equiv \uparrow$ TensorFlow               |                                                       |

|                                                     | TensorFlow Core                            | AUTOMATIC MIXED PRECISION<br>PACKAGE - TORCH.CUDA.AMP |

|                                                     | TensorFlow > Learn > TensorFlow Core > Gui | de                                                    |

#### Mixed precision

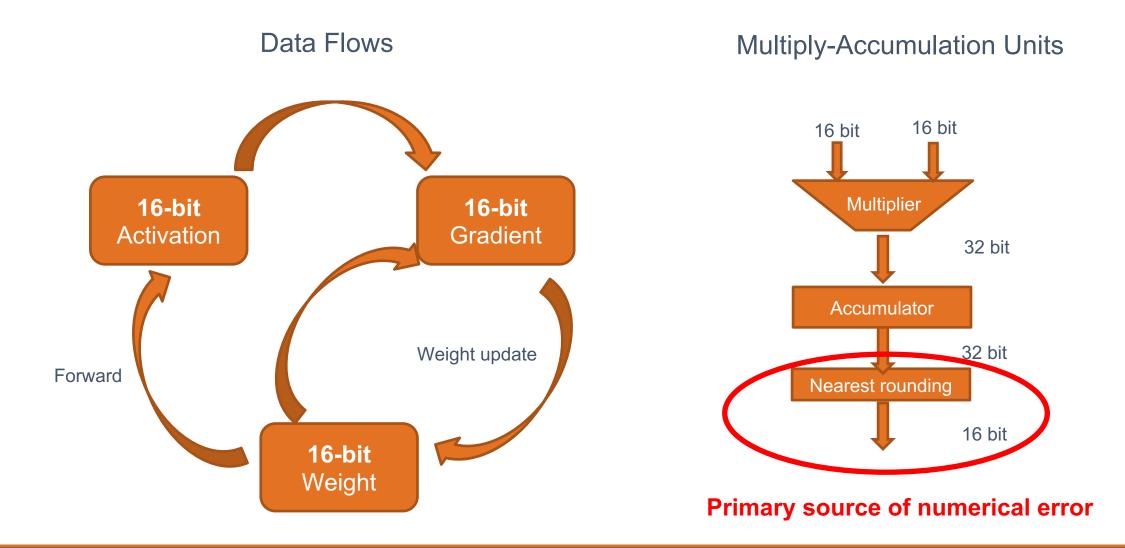

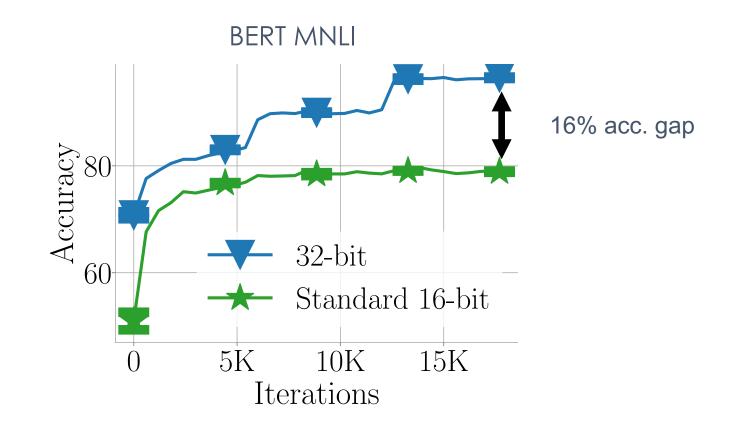

### Illusion: 16-bit FPU alone is not enough to maximize model acc.

#### Can we support only 16-bit FPU on accelerators

&

### achieve model acc. matching 32-bit training?

©2021 SambaNova Systems

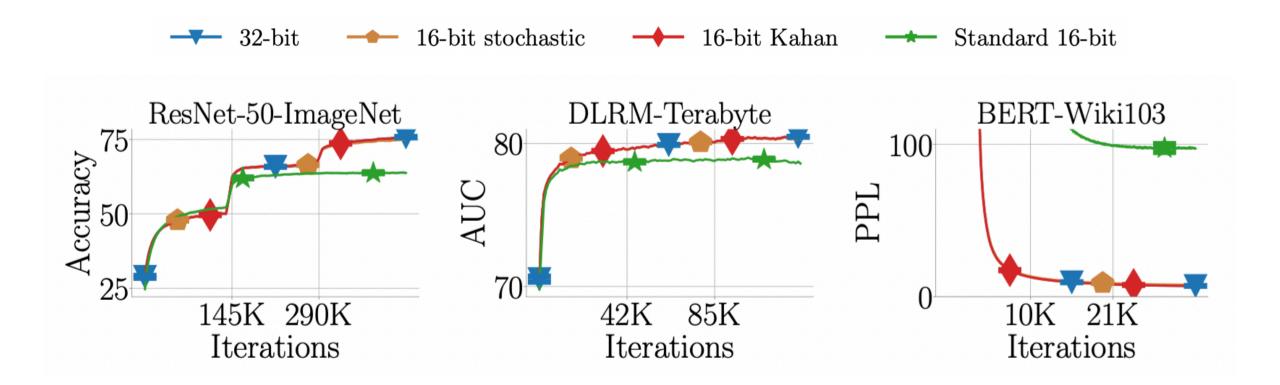

### Pure 16-bit (BFloat16) FPU Training

### **The Accuracy Challenge**

#### Standard 16-bit FPU training degrades model accuracy

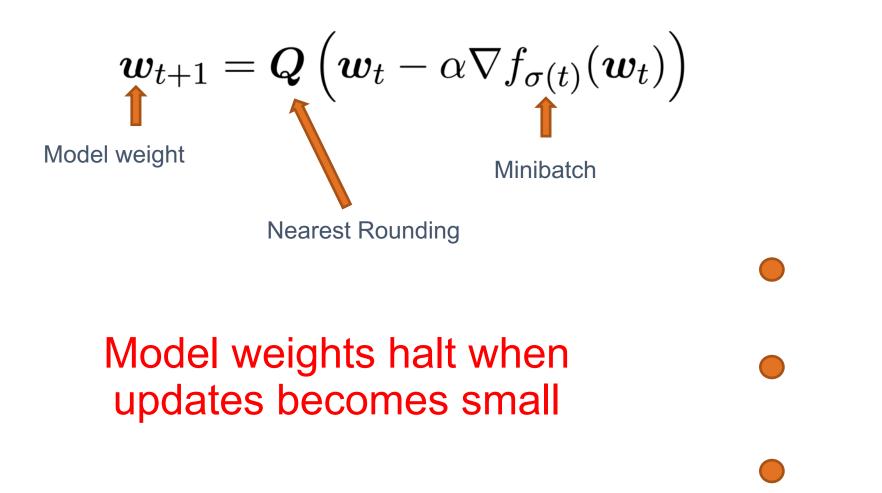

#### The Devil: Nearest Rounding(NR) for Model Weight Updates

Rounding

Update

#### The Devil: Nearest Rounding (NR) for Model Weight Updates

Theory sketch for least-squares regression

$$\|\boldsymbol{w}_{t} - \boldsymbol{w}^{*}\| \geq \mathcal{O}\left(\boldsymbol{\epsilon} \cdot \min_{j} |\boldsymbol{w}_{j}^{*}|\right)$$

Optimal solution j-th dim of the optimal solution

#### Inaccurate weight update fundamentally degrades convergence

### Stochastic Rounding to the Rescue

#### Intuition

The expectation of unbiased estimates is as accurate as weights w/o rounding

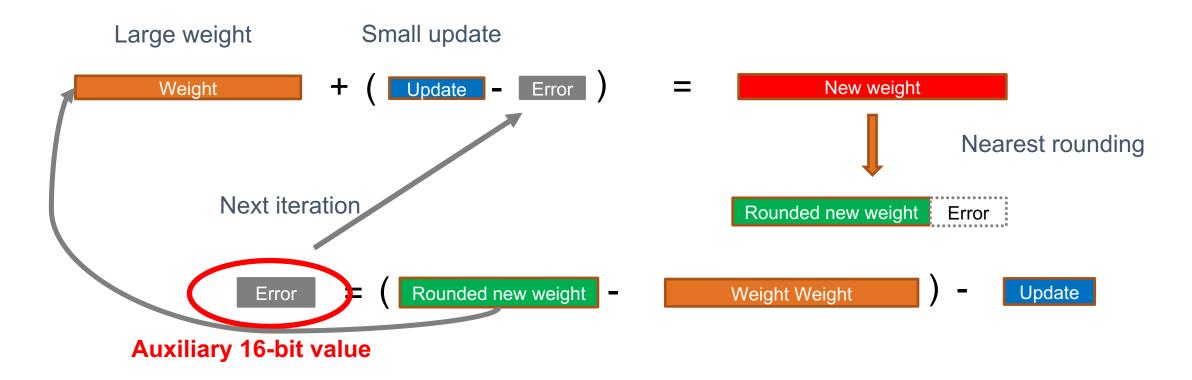

### Kahan Summation as Alternative Enhancement

Auxiliary 16-bit values to track and correct weight update errors from NR

#### Pure 16-bit training can match 32-bit training in model acc.

#### Summary

#### With support for

#### Accelerators with only 16-bit compute units can match acc. of 32-bit training

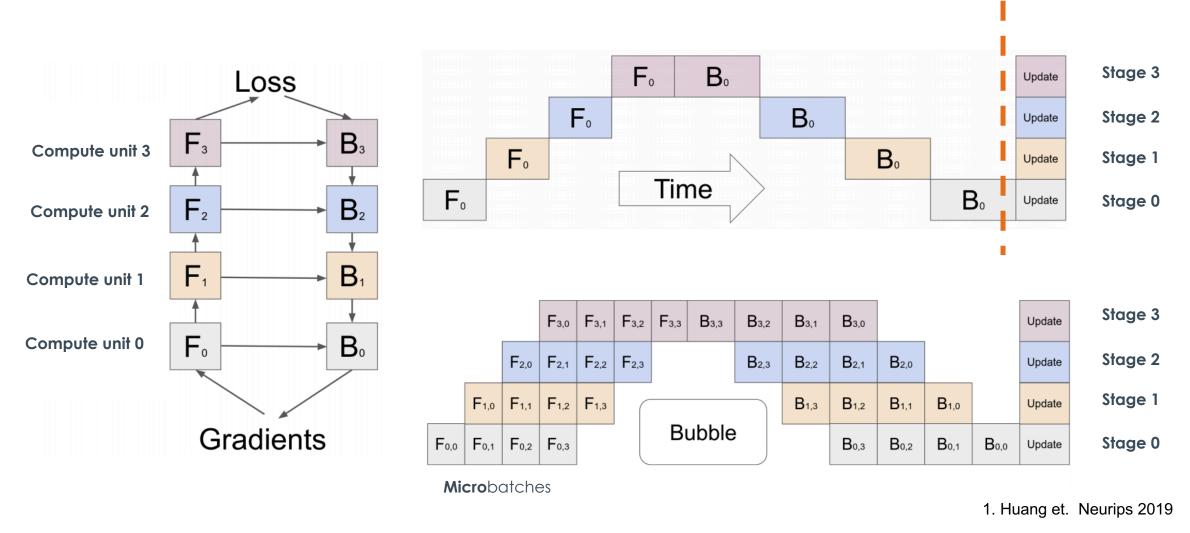

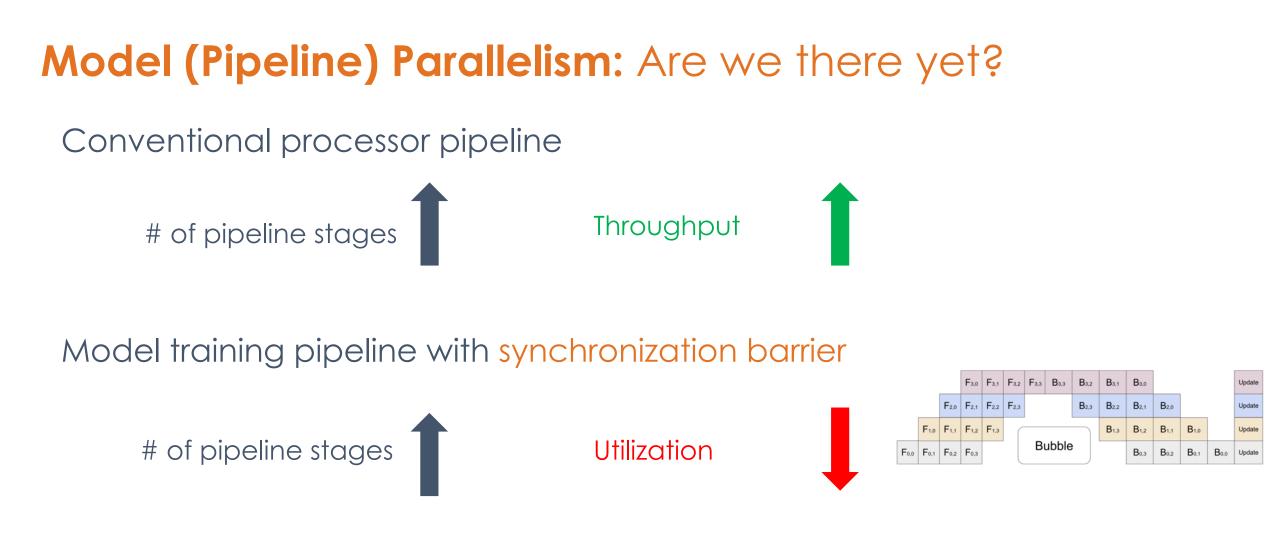

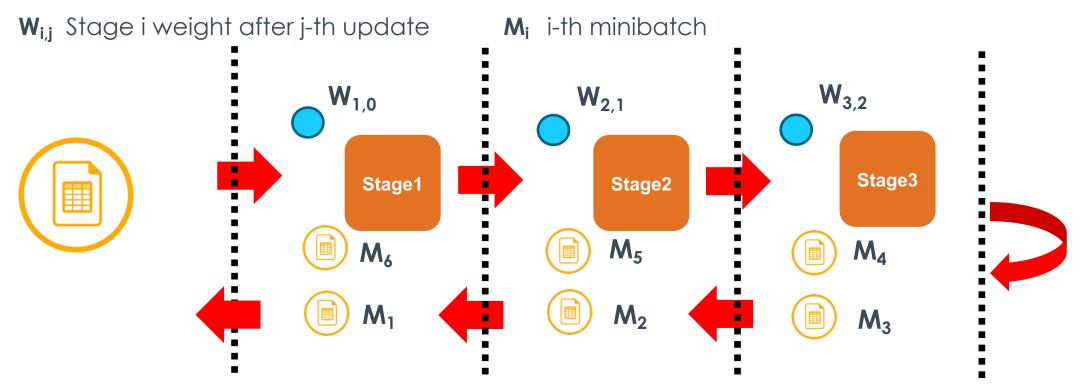

# Model (Pipeline) Parallelism

#### Synchronization barrier

#### How much utilization do we really need to sacrifice?

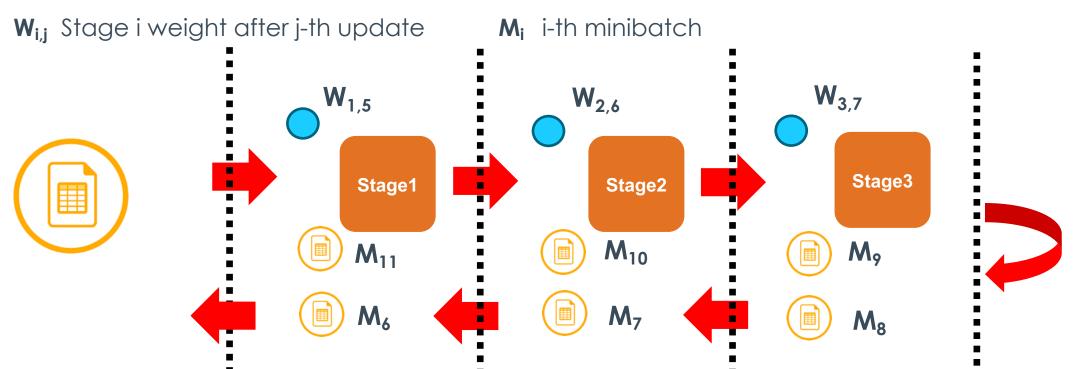

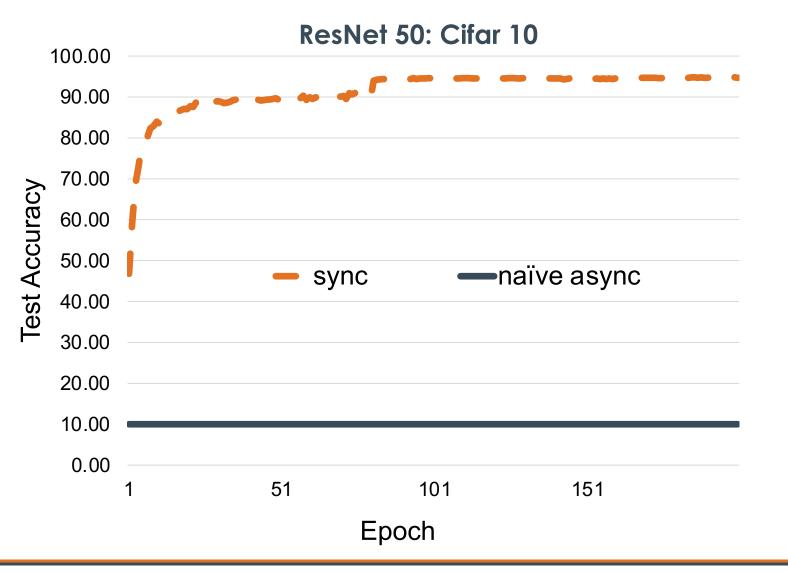

### Async. Pipeline Parallelism Steady State

Goal: No hardware sacrifices!

### Async. Pipeline Parallelism Steady State

$M_6$  uses  $W_{1,0}$  for forward and  $W_{1,5}$  for backward: delay = 5  $M_6$  uses  $W_{3,4}$  for forward and  $W_{3,5}$  for backward: delay = 1

#### Panic: Introduces different asynchrony (delays) at different stages.

### Houston, we have a problem.

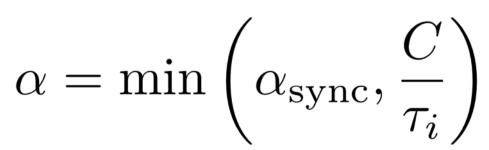

**Key Insight:** Scale your learning rate proportional to the delay.

Chris De Sa

### Maximize efficiency with no accuracy compromise

PipeMare: MLSys '20

### The SambaNova Systems Advantage

#### **Application innovations**

# Part 3. Model Innovations:

Powered by our architecture and algorithm

©2021 SambaNova Systems

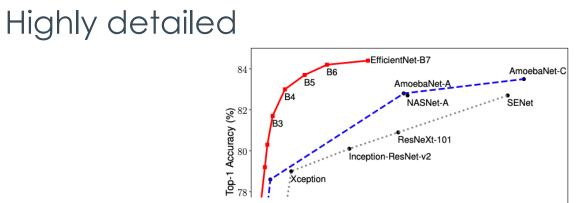

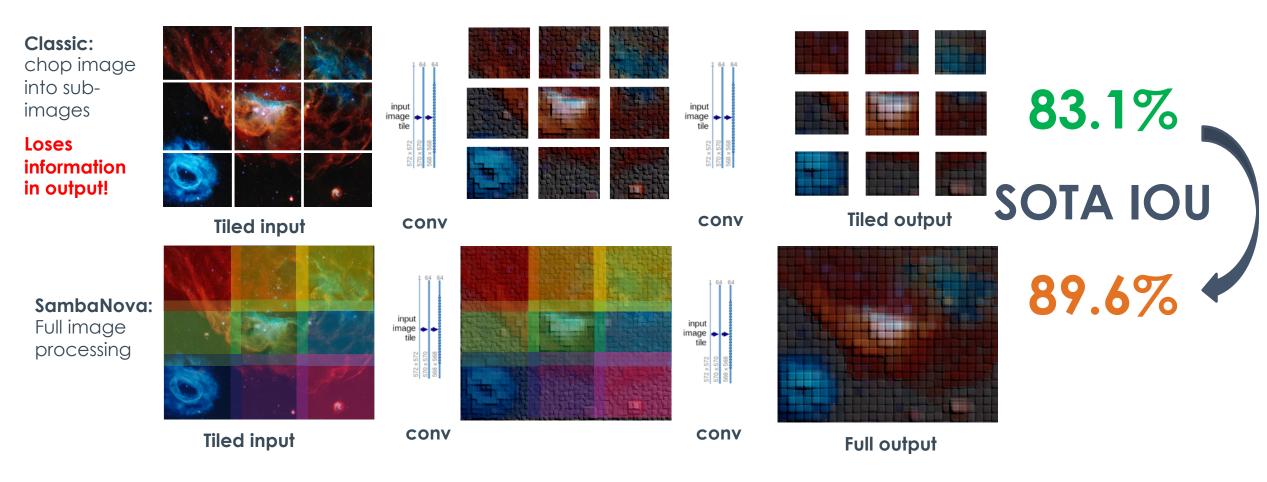

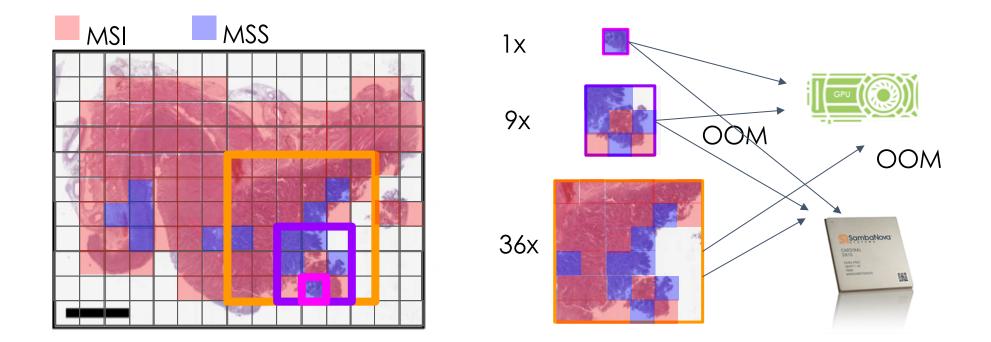

#### **Computer Vison** Evolution of high-resolution Deep Learning

Low-resolution (e.g. cats)

**4k images** (e.g. Autonomous driving)

**50k x 50k** (e.g. astronomy, medical imaging, virus, ...

# **No Compromise High-Res Segmentation**

## Training w/o information loss from full-image processing

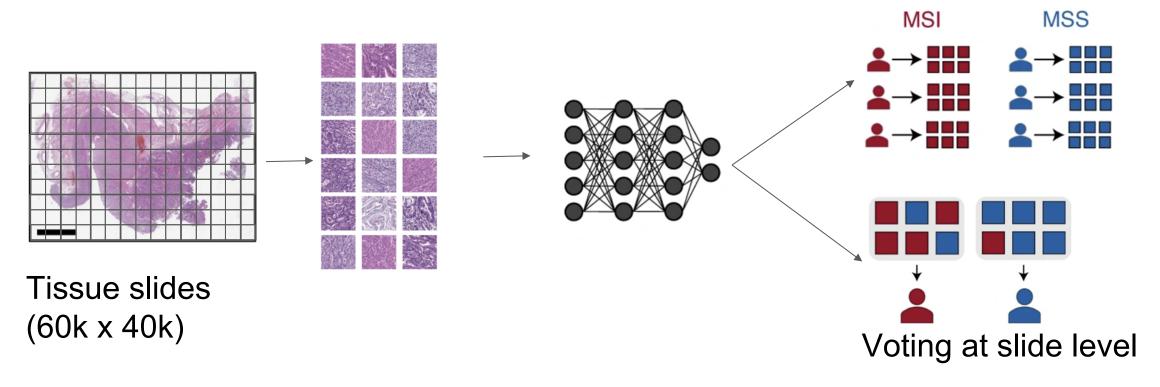

# High-Res Pathology with Slide-level Label (TCGA)

#### Train with Patch label = slide label

## Noisy patches limits model accuracy

# High-Res Pathology with Slide-level label (TCGA)

# 16X larger patches $\rightarrow$ 6 Pt higher AUC

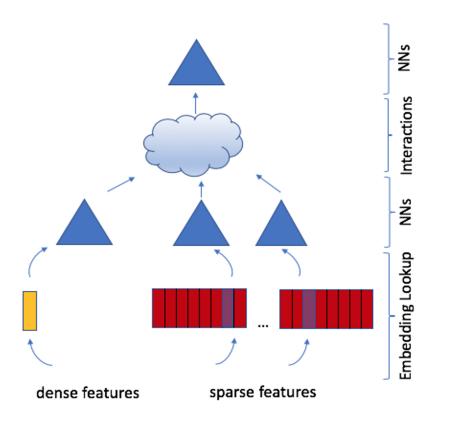

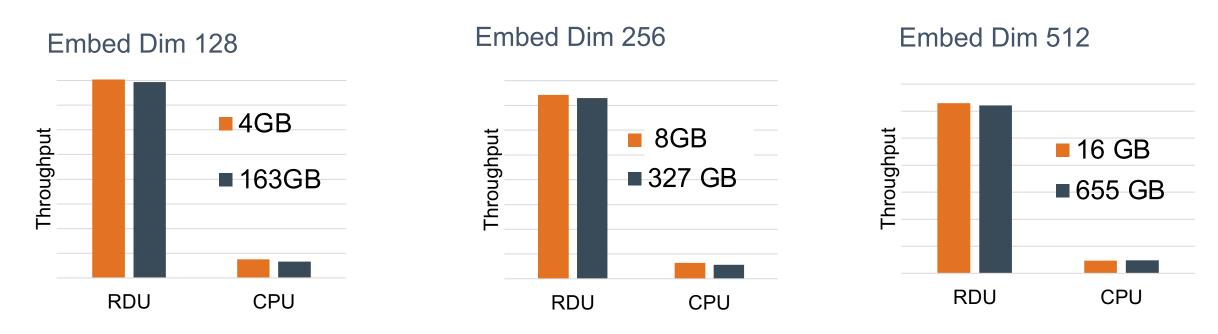

# **Recommender Models**

The backbone of many internet services

## **Recommender systems**

## Key common component: Sparse embedding feature

# **Recommender systems**

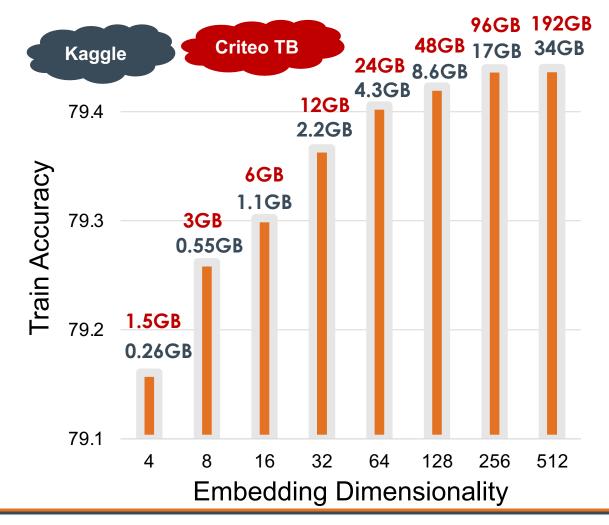

More embedding features, more accuracy

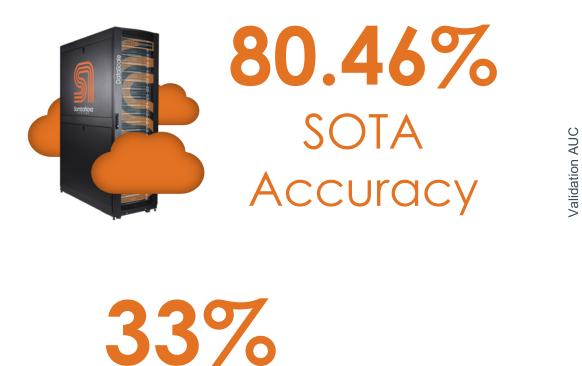

## State-of-the-art accuracy on DLRM

Faster Step-to-accuracy

0.8 0.795 0.79 1 RDU (batch size 3k, emb dim 1024) 8 GPUs (batch size 32k, emb dim 128)

40

50

% epoch

ML Perf threshold

60

70

80

90

100

World Record DLRM Training Accuracy

0.805

0.785

0.78 0

10

20

30

# Bigger isn't always better...but it is sometimes.

#### Training Performance

r5d.metal (CPU, FP32)

## SambaNova scales to training massive recommender models

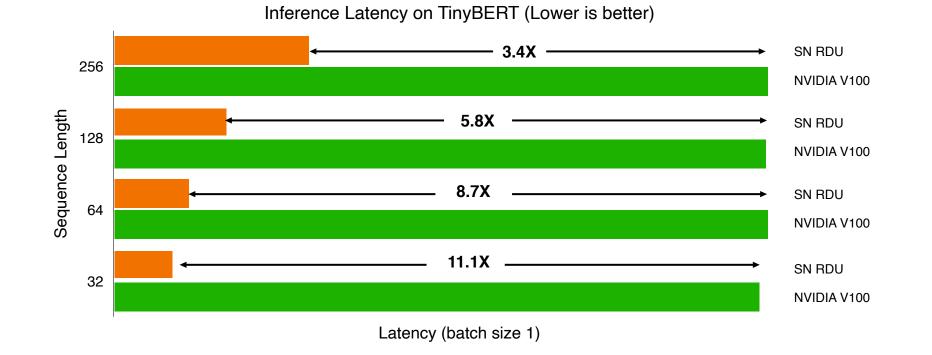

# Natural Language Processing

Breakthrough efficiency in NLP model online deployment

#### **Distilled tiny Bert model**

Short sequence input

Enable up to 11X speedup for online training and inference

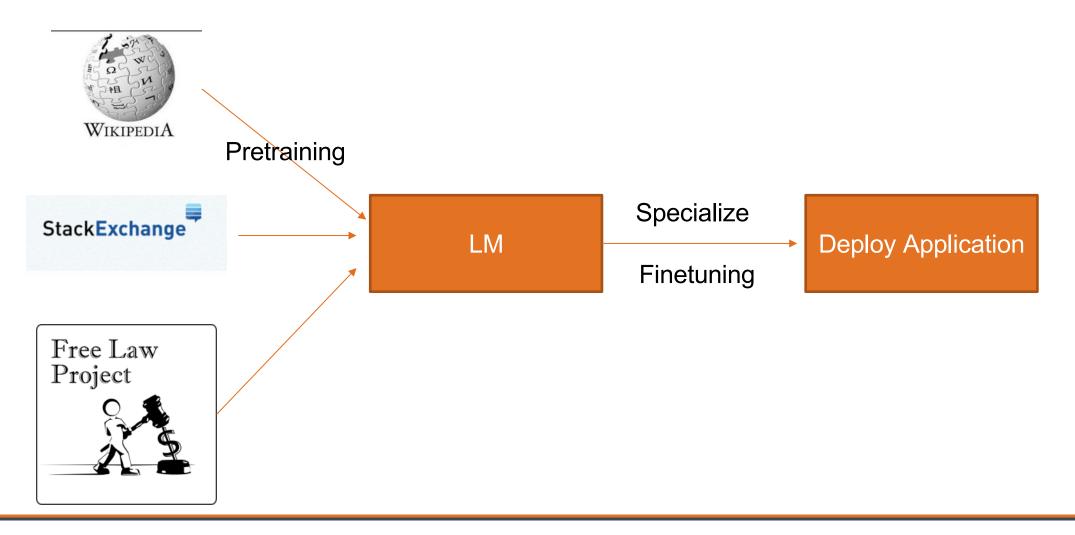

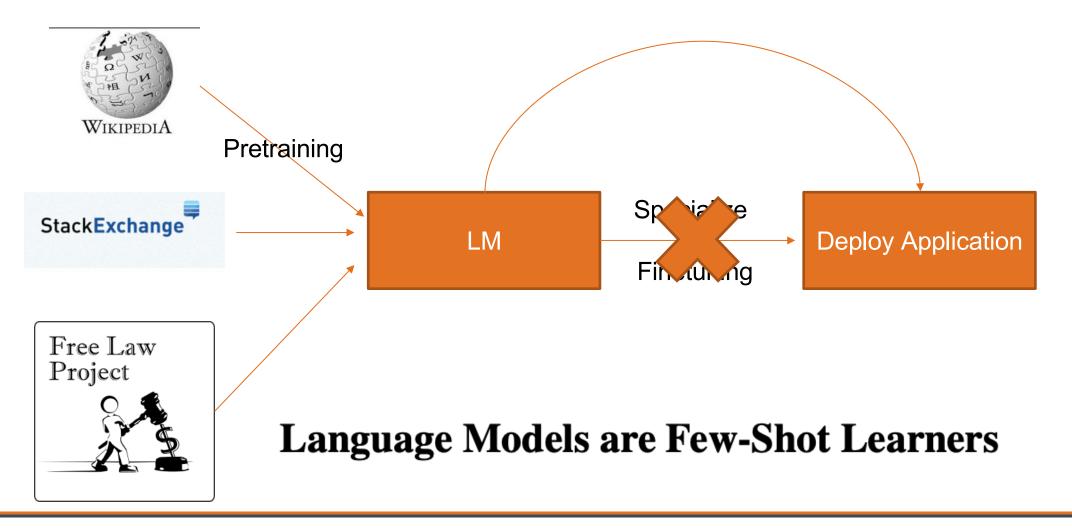

## **Pretraining and Finetuning**

©2021 SambaNova Systems

# **Domain Adaptation**

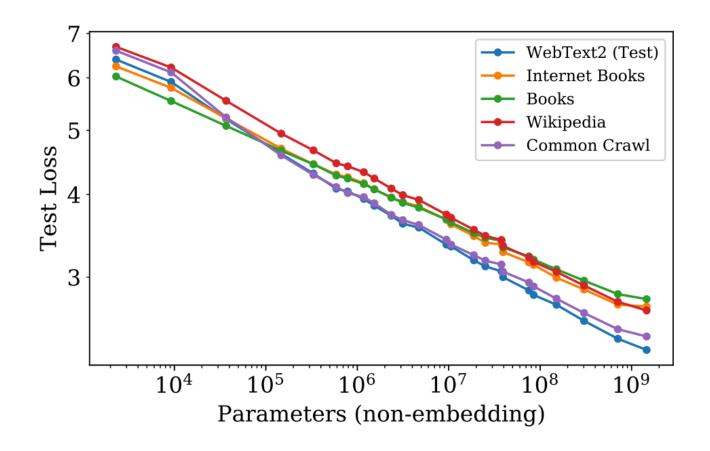

#### Scaling Laws for Neural Language Models

Application accuracy improves as the size of the language model increases

#### **Pretraining and Finetuning**

©2021 SambaNova Systems

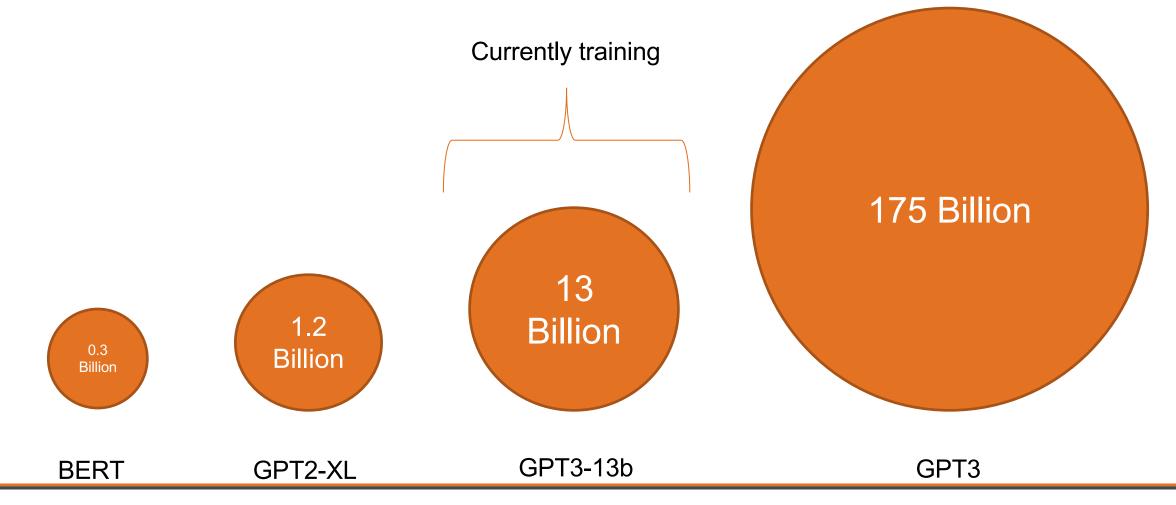

## **GPT Family**

Will start training next month

©2021 SambaNova Systems

@SambaNovaAI

sambanova-systems

sambanova.ai